## UNIVERSITI TUN HUSSEIN ONN **MALAYSIA**

# FINAL EXAMINATION SEMESTER II **SESSION 2021/2022**

COURSE NAME

: IC PACKAGING

COURSE CODE

: BEJ 43503

PROGRAMME CODE : BEJ

EXAMINATION DATE : JULY 2022

**DURATION**

: 3 HOURS

INSTRUCTION

: 1. ANSWER ALL QUESTIONS.

2. THIS FINAL EXAMINATION IS CONDUCTED VIA CLOSED BOOK

3. STUDENTS ARE **PROHIBITED** TO CONSULT THEIR OWN MATERIAL OR ANY EXTERNAL RESOURCES

**DURING THE EXAMINATION**

CONDUCTED VIA CLOSED BOOK

THIS QUESTION PAPER CONSISTS OF FIVE (5) PAGES

CONFIDENTIAL

### CONFIDENTIAL

BEJ 43503

- Q1 (a) Electronics products such as cell phone, fax machine, microwave oven, computer and calculator are based on Microsystem Technologies.

- (i) Define the term of Microsystems.

(2 marks)

- (ii) Give **FOUR (4)** evolution waves in Microsystem Technologies. (4 marks)

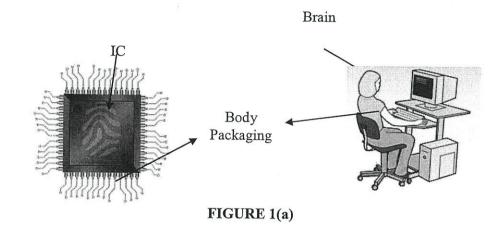

- (iii) Match FOUR (4) analogy between human body and electronic packaging as depicted in FIGURE 1(a).

(4 marks)

- (b) With the aid of a diagram, explain the processes involved in die cutting to system assembly process. (4 marks)

- (c) Packaging is needed in all IC, which are classified into Through-Hole Technology (THT) and Surface Mount Technology (SMT). Both packages have their own unique packaging process flow.

- (i) Elaborate the processes in SMT.

(4 marks)

(ii) Discuss in detail the differences between THT and SMT.

2

(2 marks)

<u>s</u>

**CONFIDENTIAL**

TERBUKA

### CONFIDENTIAL

#### BEJ 43503

- Q2 Wire bonding is the process of providing an electrical connection between the silicon chip and the external leads of the semiconductor device using very fine bonding wires.

- (i) Using diagram, discuss the bonding sequence of wire bonding process (12 marks)

- (ii) Sketch and label the ball/wedge connection.

(2 marks)

(iii) Sketch and label the ball/ball connection.

(2 marks)

(iv) Explain FOUR (4) process parameters in the wire bonding process.

(4 marks)

- Q3. Microvias are used as the interconnects between layers in high density interconnect (HDI) substrates and printed circuit boards (PCBs) to accommodate the high input/output (I/O) density of advanced packages.

- (i) List **THREE** (3) technologies involved in Microvia process (6 marks)

- (ii) Sketch and explain all technologies in Q3(a)(i)

(8 marks)

(iii) Name below type of microvias

(6 marks)

(a)

(b)

(c)

- Q4 (a) Encapsulation and sealing are two major protecting functions of IC packaging.

- (i) Explain the purpose of the encapsulation process.

(4 marks)

- (b) The encapsulation provides both chemical and mechanical protection of IC, such that a reasonable life expectancy can be achieved under field conditions in automotive, telecommunications, computer, consumer, medical and other industries.

- (i) Discuss the effect of encapsulation on the performance of electronic packaging.

- (ii) Differentiate between hermetic and non-hermetic material.

(4 marks)

(6 marks)

- (iii) State the effect of encapsulation on the performance of electronic packaging.

- (iv) Describe chemical protection of IC.

(2 marks)

(4 marks)

CONFIDENTIAL

TERBUKA

#### CONFIDENTIAL

BEJ 43503

- Q5 (a) As 5G, AI, and high-performance computing continue to make inroads into our world, there's escalating demand for semiconductor devices that deliver enhanced performance, lower latency, increased bandwidth and power efficiency. 2.5D & 3D technologies deliver that and more.

- (i) Define 2.5D and 3.0 D IC packaging

(4 marks)

(ii) Discuss the benefits of 2.5D and 3.0D

(6 marks)

- (b) High-temperature operating life (HTOL) is a reliability test applied to integrated circuits (ICs) to determine their intrinsic reliability. This test stresses the IC at an elevated temperature, high voltage and dynamic operation for a predefined period of time.

- (i) Explain High-temperature operating life (HTOL)

(4 marks)

(ii) Describe the process of HTOL

(6 marks)

- END OF QUESTIONS-