## UNIVERSITI TUN HUSSEIN ONN MALAYSIA

# **FINAL EXAMINATION** SEMESTER II **SESSION 2016/2017**

COURSE NAME

: ELECTRONICS I

COURSE CODE

: BWC 10703

PROGRAMME CODE : BWC

EXAMINATION DATE : JUNE 2017

**DURATION**

3 HOURS

INSTRUCTION

ANSWERS ALL QUESTIONS

TERBUKA

THIS QUESTION PAPER CONSISTS OF FIVE (5) PAGES

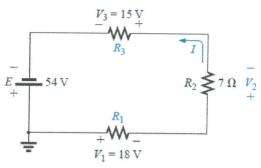

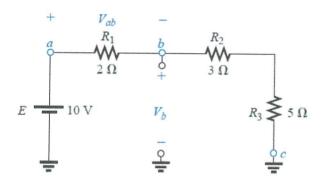

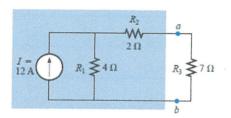

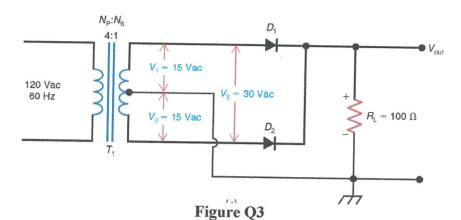

Q1 (a) Describe Kirchoff's Voltage Law (2 marks) (b) As to Figure Q1(b) is considered, determine  $V_2$  using KVL (ii) calculate I (iii) find  $R_1$  and  $R_3$ (8 marks) (c) For the network of Figure Q1(c), by using voltage divider rule calculate  $V_{ab}$ (i) (ii) determine  $V_b$ (iii) calculate  $V_c$ (10 marks) **O2** (a) State the The'venin's Theorem (2 marks) (b) Find the The'venin equivalent circuit for in the shaded area of the network in Figure Q2(b) (10 marks) What is a semiconductor? How it can be compared with a conductor and an (c) (i) Describe forward and reverse biased of a diode (ii) [Diagrams might help in these questions] (8 marks) Q3 Figure Q3 shows the full wave rectifier circuit.  $T_1$  is a step down transformer, which provides the secondary voltage. This transformer secondary is called as center tapped. In this figure, each half of the secondary has a voltage of 15  $V_{ac}$ , which is one half the total secondary voltages,  $V_S$ , of 30  $V_{ac}$ . The voltage for the top half of the secondary is designated  $V_1$ , whereas the voltage for the bottom half of the secondary is designated  $V_2$ . Analyze; (a) top half of secondary voltage  $V_{I}$ , (6 marks) TERBUKA bottom half of secondary voltage,  $V_2$ , (b) (2 marks) (c) output voltage produced when  $D_1$  is conducted. (4 marks) (d) output voltage produced when  $D_2$  is conducted. (2 marks)

### CONFIDENTIAL

BWD 10703

| (e) | the combination output voltage produced by $D_1$ and $D_2$ and value of $I_L$ . |           |

|-----|---------------------------------------------------------------------------------|-----------|

|     |                                                                                 | (6 marks) |

Q4 (a) Explain the function of emitter and collector regions in a transistor.

(2 marks)

(b) For the circuit shown in **Figure Q4(b)**, calculate the value for  $V_B$ ,  $V_E$ ,  $I_C$ ,  $V_{CE}$ ,  $I_{C(sat)}$  and  $V_{CE(off)}$ . Then, construct a dc load line showing the value of  $I_{C(sat)}$ ,  $V_{CE(off)}$ ,  $I_{CQ}$  and  $V_{CEQ}$ .

(18 marks)

- **Q5** (a) Draw the schematic symbol of JFETs

- (i) n-channel symbol

- (ii) offset-gate symbol

- (iii) p-channel symbol

(6 marks)

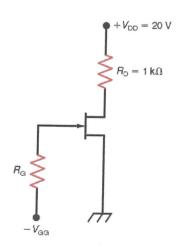

(b) Assume that the JFET circuit in **Figure Q5(b)** is to be mass produced. The JFET has the following parameters:

| <u>Parameter</u> | <u>Minimum</u> | <u>Maximum</u> |

|------------------|----------------|----------------|

| $I_{DSS}$        | 2 mA           | 20 mA          |

| $V_{GS(off)}$    | -2 V           | -8 V           |

Calculate the minimum and maximum value for  $I_D$  and  $V_{DS}$  if  $V_{GS} = -1.5$  V for the range of JFET parameters shown and conclude the finding.

(14 marks)

## **TERBUKA**

#### **FINAL EXAMINATION**

SEMESTER / SESSION : SEM II / 2016/2017 COURSE NAME : ELECTRONICS I

FCTRONICS I PROGRAMME COL

PROGRAMME CODE : BWC COURSE CODE : BWC 10703

Figure Q1(b)

Figure Q1(c)

Figure Q2(b)

. H.E. NGOZE ELECTIC GEL. "NE EGG Parevacen Lauren Fakulti Sair et Tearre ugenar Hombanguran Jusar Universit Fer Hugseyn Fono Mwaresto

### **FINAL EXAMINATION**

SEMESTER / SESSION : SEM II / 2016/2017 **COURSE NAME**

: ELECTRONICS I

PROGRAMME CODE: BWC

COURSE CODE : BWC 10703

$+V_{\rm CC} = 18 \text{ V}$  $R_{\rm C}=1.5~{\rm k}\Omega$  $R_1 = 33 \text{ k}\Omega$  $\beta_{\rm dc}=200$  $R_2 = 5.6 \text{ k}\Omega$  $R_{\rm F}=390~\Omega$

Figure Q4(b)

Figure Q5(b)

Челзуасть Кангр Рахил Sains, Тетельку овы Ремациориль Тичас Прочесть Тет Ньзав Сент Мацията