# **UNIVERSITI TUN HUSSEIN ONN MALAYSIA**

# FINAL EXAMINATION SEMESTER I SESSION 2009/2010

: BEE 3233

: 3 HOURS

SUBJECT NAME

: MICROPROCESSOR AND MICROCONTROLLER

SUBJECT CODE

COURSE : 3 BEE

DATE OF EXAMINATION : NOVEMBER 2009

DURATION

INSTRUCTIONS

: ANSWER ALL QUESTIONS IN PART A AND ANY TWO (2) QUESTIONS IN PART B

THIS PAPER CONSIST OF 21 PAGES

### PART A

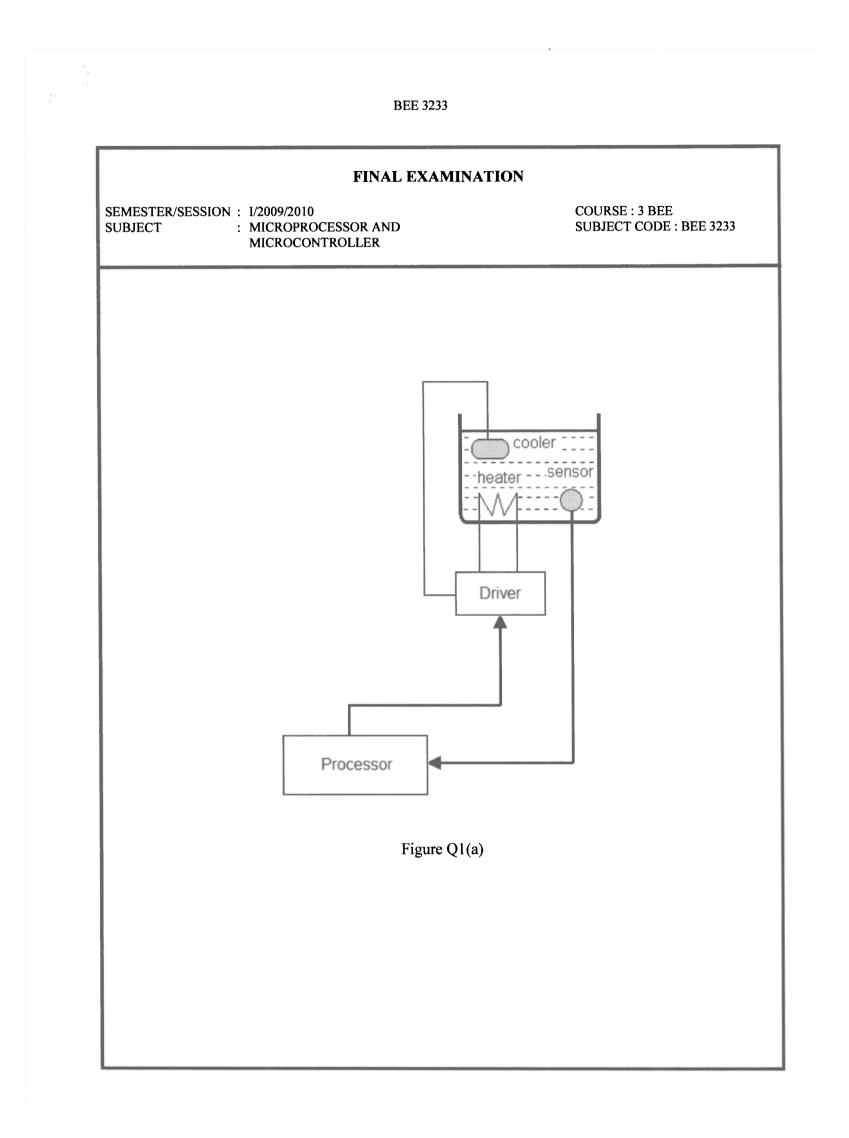

Q1 (a) Figure Q1(a) shows a temperature monitoring system in a plant. What is the best processor for the system (microprocessor or microcontroller)? Give three reasons why do you choose that technology.

(5 marks)

(b) Sketch the circuit of the system in Question 1(a) above by showing the connection between the processor, driver and sensor.

(5 marks)

- (c) Parity is a very simple method of error detection in serial communication technique. If parity is enabled, it is declared to be whether Odd or Even parity. Determine the value of the data if we want to transmit the ASCII character as below. Given the transmission system uses one start bit (logic low), one stop bit (logic high) and an Odd parity.

- i) Character 'A'

- ii) Character 'C'

(4 marks)

- (d) Figure Q1(d) shows a complete program of transferring an ASCII character using serial communication technique. Analyze the program and answer the following questions:

- i) What is the first address of the program?

- ii) Calculate the duration of stop bit, T and the speed of the transmission if clock frequency is 4MHz.

- iii) What is the transmission pin of the P16F84A microcontroller?

- iv) Sketch the signal on the transmission pin.

(11 marks)

Q2 (a) Why a subroutine must not be terminated with a GOTO instruction? What instructions can be used to terminate a subroutine in the PIC 16F84A?

(3 marks)

- (b) Figure Q2(b) shows the implementation of a look-up table in PIC 16F84A assembly program. The data returned from the table is determined by reading RA0, RA1 and RA2 of PORTA.

- i) Evaluate the BINARY number output to PORTB for each of the table entries.

- ii) Explain the use of the ANDLW H'07' instruction in the above code.

- (10 marks)

- (c) Write a subroutine to use Timer 0 to create a fixed time delay of  $1000 \ \mu s$  (1 ms). You may assume that the crystal frequency is 4MHz and that the prescaler is free for use as a  $\div 4$  frequency divider. You can ignore any delays introduced by the synchronizing circuit.

(12 marks)

### PART B

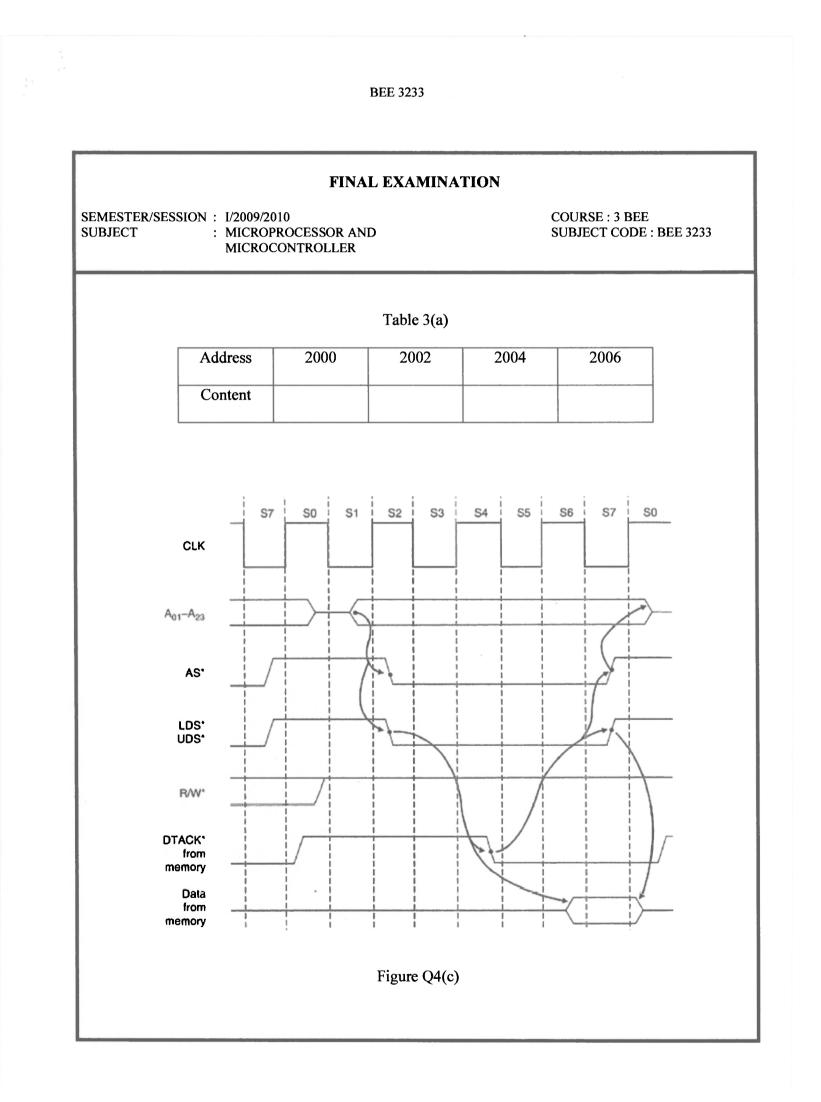

Q3 (a) Figure Q3(a) shows the MC68000's assembly program written in EASY68K simulation software. Analyze the program and answer the following questions:

- i) After the program is assembled, what is the first address of the program and the data respectively?

- ii) After the program is executed, write the value of the data in the Table 3(a) for the given address.

- iii) What is content of the CCR (Conditions Code Register) after the microprocessor executes the ADD.W Numbers+4, D0 instruction?

Move

iv) What are the addressing modes for instruction ADD.W Numbers, D0?

(12 marks)

(b) What is the difference between MOVE.B #50,D0 and MOVEQ #50,D0? Which instruction to be used if the data is 32-bit and the application has limited memory location to store the program?

(5 marks)

(c) Write a sequence of MC68000's instructions to compare two unsigned byte value located in memory. The first byte is located in \$2000, and the second byte is located in \$2001. Store the bigger value in address location \$2002.

(8 marks)

#### Q4 Solve the following problems on MC68000 microprocessor system:

(a) Give a reason when you might prefer JSR or BSR in a program.

(4 marks)

(b) Write MC68000's assembly program to implement the following algorithm:

D3 = 0; D4 = 5; While (D3 < D4) { D3 = D3 + 1; }

(6 marks)

(c) Based on Figure Q4(c), answer the following question for the read cycles of 68000:

- i) In the read cycle timing diagram shown in Figure Q4(c), which of the signals are driven by the processor?

- ii) The data strobes effectively encode three pieces of information for a bus read. Name two of them.

- iii) In the read cycle, AS\* and UDS\*/LDS\* are asserted simultaneously. In a write cycle, UDS\*/LDS\* are asserted approximately one cycle after AS\*. Why?

(5 marks)

(d) A ROM of 1Kbyte (organized as two 512byte), SRAM of 64Kbyte (organized as two 32K), DRAM of 1Mbyte (organized as two 512K) and a peripherals (PERI) device uses 16 bytes of storage are used in a MC68000 microprocessor system. Design a partial decoder (including memory map) for the system by using A<sub>23</sub> and A<sub>22</sub> as an input to be decoded. Your design must show other inputs of the decoder (eg: LDS\*/UDS\*, AS\*) and one output CS\* to indicate how the system will choose an active device at one time clearly.

(10 marks)

Q5 (a) List five Special Function Registers (SFR) and explain the function of each register that you listed.

(5 marks)

- (b) Write a PIC16F84A assembly language based on the statement below:

- i) Select BANK1.

- ii) Initialize the Port if RA1 and RA2 are connected to the switches while RB3, RB4 and RB5 are connected to LEDs.

- iii) Move 50H to file register 30H.

- iv) Move 8-bit of data from file register named REG1 to another file register name REG2.

- v) Subtract 5 from file register 30H, if the content of 30H is not zero, repeat the subtraction.

(7 marks)

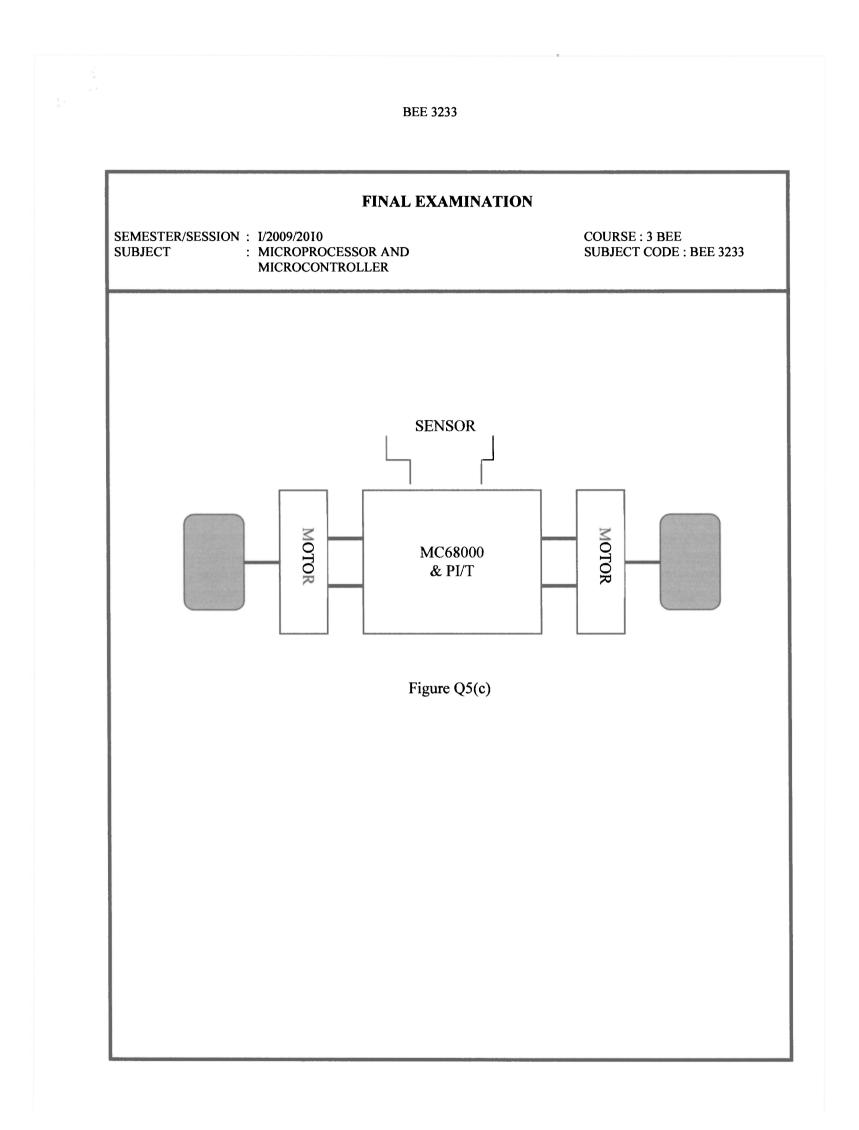

(c) MC68000 microprocessor is used as a main processor in a mobile robot as shown in Figure Q5(c). The robot has two wheels controlled by two DC motors. To move a robot forward, send \$40 to Port B Data Register (PBDR) of PI/T. To move the robot backward, send \$80 to Port B Data Register (PBDR) of PI/T. To stop the robot, send \$00 to PBDR of PI/T. Given the address of the PBDR is at \$800012 and a one second delay subroutine as below.

| Delay | MOVE.L | #551800,D1 |

|-------|--------|------------|

| DEL   | SUBQ.L | D1         |

|       | BNE    | DEL        |

|       | RTS    |            |

- i) Write a program to move robot forward for five seconds, then stop for two seconds and then move backward for five seconds.

- ii) List two advantages of using the direct current (DC) motor in robot applications.

(13 marks)

|                | FI                                                                | NAL EXAMINATIO                                       | N |

|----------------|-------------------------------------------------------------------|------------------------------------------------------|---|

|                | /2010<br>OPROCESSOR<br>OCONTROLLE                                 | COURSE : 3 BEE<br>SUBJECT CODE : BEE 323             |   |

| PORTB<br>TxReg | EQU<br>EQU                                                        | 06H<br>20H                                           |   |

|                | ORG<br>MOVLW<br>TRIS                                              | 0H<br>0x0<br>PORTB                                   |   |

| start          | Movlw<br>Movwf<br>Call<br>Movlw                                   | 'A'<br>TxReg<br>SEND<br>'B'                          |   |

|                | MOVWF<br>CALL<br>GOTO                                             | TxReg<br>SEND<br>stop                                |   |

| SEND           | BCF<br>CALL                                                       | PORTB,0<br>Delay                                     |   |

|                | local<br>while<br>BTFSC<br>CALL<br>BTFSS<br>CALL<br>i=i+1<br>endw | i=0<br>i<8<br>TxReg,i<br>SEND_1<br>TxReg,i<br>SEND_0 |   |

|                | BSF<br>CALL<br>CALL<br>RETURN                                     | PORTB,0<br>Delay<br>Delay                            |   |

| SEND_1         | BSF<br>CALL<br>RETURN                                             | PORTB,0<br>Delay                                     |   |

| SEND_0         | BCF<br>CALL<br>RETURN                                             | PORTB,0<br>Delay                                     |   |

| Delay          | MOVLW<br>MOVWF                                                    | d'33'<br>30H                                         |   |

| loop           | DECFSZ<br>GOTO<br>RETURN<br>END                                   | 30Н<br>10ор                                          |   |

| TER/SESSION :<br>CT : | MICROPR |                 |                        | COURSE : 3 BEE<br>SUBJECT CODE : BEE 323 |

|-----------------------|---------|-----------------|------------------------|------------------------------------------|

|                       |         |                 |                        |                                          |

| STO                   | RE 1    | EQU             | н' 59'                 |                                          |

| LOO                   |         | MOVF            |                        |                                          |

|                       |         | ANDLW           | PORTA,W<br>H'07'       |                                          |

|                       |         | CALL            | TABLE                  |                                          |

|                       |         | MOVWF           | PORTB                  |                                          |

|                       |         | GOTO            | LOOP                   |                                          |

| TAB                   | LE      | ADDWF           | PCL,F                  |                                          |

|                       | 1       | RETLW           | D'255'                 |                                          |

|                       |         | RETLW           | 0                      |                                          |

|                       |         | RETLW           | H'9F'                  |                                          |

|                       |         | RETURN          |                        |                                          |

|                       |         | RETLW           | `Z'                    |                                          |

|                       |         | GOTO<br>RETLW   | OTHER<br>H'7C'         |                                          |

|                       |         | RETLW           | `a'                    |                                          |

| OTH                   |         | RETLW           | STORE                  |                                          |

|                       |         |                 | F' 02(1)               |                                          |

|                       |         |                 | Figure Q2(b)           |                                          |

| COD                   | E       | EQU             | \$1000                 |                                          |

| DAT                   |         | EQU             | \$2000                 |                                          |

|                       |         |                 |                        |                                          |

|                       |         | ORG             | CODE                   |                                          |

| PRO                   |         | MOVE.W          | NUMBERS, DO            |                                          |

|                       |         | ADD.W           | NUMBERS+2,D0           |                                          |

|                       |         | ADD.W<br>MOVE.W | NUMBERS+4,D0<br>D0,SUM |                                          |

|                       | 1       | W. HVUL         | DO, SOM                |                                          |

|                       |         | ORG             | DATA                   |                                          |

| NUM                   |         | DC.W            | \$0011                 |                                          |

|                       |         | DC.W            | \$0022                 |                                          |

|                       |         | DC.W            | \$0033                 |                                          |

| SUM                   |         | DC.W            | 0                      |                                          |

|                       |         | END             | PROG                   |                                          |

|      | СТ                   | MICE       | ROPROCE<br>ROCONTR           | OLLER       |                | File Sum     | mary f      | SUI     | URSE : 3<br>3JECT CC | DDE : F              | 3EE 3: | 233               |

|------|----------------------|------------|------------------------------|-------------|----------------|--------------|-------------|---------|----------------------|----------------------|--------|-------------------|

| Addr | Name                 | Bit 7      | Bit 6                        | Bit 5       | Bit 4          | Bit 3        | Bit 2       | Bit 1   | Bit 0                | Value<br>Powe<br>RES | r-on   | Details<br>on pag |

| Bank | 0                    | L          |                              |             | <u> </u>       |              |             |         | L                    | L                    |        |                   |

| 00h  | INDF                 | Uses con   | tents of FSF                 | R to addre  | ess Data Mem   | ory (not a p | hysical reg | jister) |                      |                      |        | 11                |

| 01h  | TMRO                 |            | -bit Real-Time Clock/Counter |             |                |              |             |         |                      | хххх                 | хххх   | 20                |

| 02h  | PCL                  | Low Orde   | r 8 bits of th               | ne Progra   | m Counter (PC  | C)           |             |         |                      | 0000                 | 0000   | 11                |

| 03h  | STATUS(2)            | IRP        | RP1                          | RP0         | то             | PD           | Z           | DC      | С                    | 0001                 | 1xxx   | 8                 |

| 04h  | FSR                  | Indirect D | ata Memory                   | Address     | Pointer 0      |              |             |         | L                    | XXXX                 | xxxx   | 11                |

| 05h  | PORTA <sup>(4)</sup> | _          | _                            |             | RA4/T0CKI      | RA3          | RA2         | RA1     | RAO                  | x                    | xxxx   | 16                |

| 06h  | PORTB <sup>(5)</sup> | RB7        | RB6                          | RB5         | RB4            | RB3          | RB2         | RB1     | RB0/INT              | xxxx                 | xxxx   | 18                |

| 07h  | _                    | Unimplen   | nented locat                 | tion, read  | as '0'         |              |             |         | 1                    | -                    | -      | -                 |

| 08h  | EEDATA               | EEPRON     | EEPROM Data Register         |             |                |              |             |         |                      |                      | хххх   | 13,14             |

| 09h  | EEADR                | EEPRON     | EEPROM Address Register      |             |                |              |             |         |                      | хххх                 | хххх   | 13,14             |

| 0Ah  | PCLATH               | _          | _                            |             | Write Buffer   | for upper 5  | bits of the | PC(1)   |                      | 0                    | 0000   | 11                |

| 0Bh  | INTCON               | GIE        | EEIE                         | TOIE        | INTE           | RBIE         | TOIF        | INTE    | RBIF                 | 0000                 | 000x   | 10                |

| Bank | 1                    |            |                              |             |                |              |             |         | 1                    |                      |        |                   |

| 80h  | INDF                 | Uses Cor   | ntents of FS                 | R to addr   | ess Data Mem   | ory (not a p | hysical re  | gister) |                      |                      |        | 11                |

| 81h  | OPTION_REG           | RBPU       | INTEDG                       | TOCS        | TOSE           | PSA          | PS2         | PS1     | PS0                  | 1111                 | 1111   | 9                 |

| 82h  | PCL                  | Low orde   | r 8 bits of P                | rogram C    | ounter (PC)    |              |             |         | L                    | 0000                 | 0000   | 11                |

| 83h  | STATUS (2)           | IRP        | RP1                          | RP0         | ТО             | PD           | Z           | DC      | С                    | 0001                 | 1xxx   | 8                 |

| 84h  | FSR                  | Indirect d | ata memory                   |             |                |              |             |         | Į                    | xxxx                 |        | 11                |

| 85h  | TRISA                | -          | _                            | _           | PORTA Data     | Direction F  | Register    |         |                      |                      | 1111   | 16                |

| 86h  | TRISB                | PORTB      | Data Directio                | on Regist   |                |              |             |         |                      | 1111                 |        | 18                |

| 87h  | _                    | Unimpler   | nented loca                  | tion, read  | l as '0'       |              |             |         |                      | -                    | _      | -                 |

| 88h  | EECON1               | -          | _                            | _           | EEIF           | WRERR        | WREN        | WR      | RD                   | 0                    | x000   | 13                |

| 89h  | EECON2               | EEPRON     | Control Re                   | egister 2 ( | not a physical | register)    |             |         |                      |                      |        | 14                |

| 0Ah  | PCLATH               | _          | _                            | _           | Write buffer t | for upper 5  | bits of the | PC(1)   |                      | 0                    | 0000   | 11                |

| 0Bh  | INTCON               | GIE        | EEIE                         | TOIE        | INTE           | RBIE         | TOIF        | INTE    | RBIF                 | 0000                 |        |                   |

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter. but the contents of PC<12:8> are never transferred to PCLATH.

2: The TO and PD status bits in the STATUS register are not affected by a MCLR Reset.

3: Other (non power-up) RESETS include: external RESET through MCLR and the Watchdog Timer Reset.

4: On any device RESET, these pins are configured as inputs.5: This is the value that will be in the port output latch.

|                   |                                                                                                                        |                                       | FINAL         | EXAMIN         | NATION                    |                              |              |              |

|-------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------|----------------|---------------------------|------------------------------|--------------|--------------|

| EMESTER<br>UBJECT |                                                                                                                        | 2009/2010<br>IICROPROCE<br>IICROCONTR |               |                | SE : 3 BEE<br>CT CODE : E | BEE 3233                     |              |              |

|                   |                                                                                                                        | S                                     | TATUS R       | egister of     | PIC16F84                  | A                            |              |              |

|                   | R/W-0                                                                                                                  | R/W-0                                 | R/W-0         | R-1            | R/W-x                     | R/W-x                        | R/W-x        |              |

|                   | IRP                                                                                                                    | RP1                                   | RP0           | ТО             | PD                        | Z                            | DC           | С            |

|                   | bit 7                                                                                                                  |                                       |               |                |                           |                              |              | bit (        |

| bit 7-6           | Unimplem                                                                                                               | ented: Main                           | tain as 'o'   |                |                           |                              |              |              |

| bit 5             | -                                                                                                                      | ster Bank Se                          |               | ed for dire    | ct addressin              | <b>a</b> )                   |              |              |

|                   | 01 = Bank                                                                                                              | 1 (80h - FFh                          | )             |                |                           |                              |              |              |

| 1. 1. A           |                                                                                                                        | 0 (00h - 7Fh                          | )             |                |                           |                              |              |              |

| bit 4             | <b>TO</b> : Time-o                                                                                                     | out bit<br>bower-up, CL               | owny instru   | iction or g    |                           | rtion                        |              |              |

|                   |                                                                                                                        | T time-out of                         |               |                |                           |                              |              |              |

| bit 3             | PD: Power-down bit                                                                                                     |                                       |               |                |                           |                              |              |              |

|                   | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul> |                                       |               |                |                           |                              |              |              |

| bit 2             | Z: Zero bit                                                                                                            |                                       | STREP HI2     |                |                           |                              |              |              |

|                   |                                                                                                                        | esult of an ari                       | thmetic or l  | ogic opera     | tion is zero              |                              |              |              |

|                   |                                                                                                                        | esult of an ari                       |               | •              |                           |                              |              |              |

| bit 1             | DC: Digit o<br>is reversed                                                                                             | arry/borrow b                         | dit (addwf, i | ADDLW, SU      | BLW, SUBWF                | instructions)                | (for borrow, | the polarit  |

|                   |                                                                                                                        | y-out from th                         | e 4th Iow oi  | rder bit of t  | he result oc              | curred                       |              |              |

|                   |                                                                                                                        | rry-out from t                        |               |                |                           |                              |              |              |

| bit 0             | C: Carry/b<br>reversed)                                                                                                | orrow bit (AI                         | DWF, ADDL     | W, SUBLW,      | SUBWF INS                 | tructions) (fo               | r borrow. th | e polarity i |

|                   | ,                                                                                                                      | y-out from th                         | e Most Sigr   | nificant bit ( | of the result             | occurred                     |              |              |

|                   | o = No ca                                                                                                              | rry-out from t                        | the Most Sig  | gnificant bi   | t of the resu             | It occurred                  |              |              |

|                   | Note:                                                                                                                  |                                       | RF, RLF) in   | structions,    | -                         | complement<br>aded with eith |              | •            |

|                   |                                                                                                                        |                                       | -             |                |                           |                              |              |              |

|                   |                                                                                                                        |                                       |               |                |                           |                              |              |              |

|                   |                                                                                                                        |                                       |               |                |                           |                              |              |              |

|                   |                                                                                                                        |                                       |               |                |                           |                              |              |              |

| EMESTER/<br>UBJECT |                                                                                                                                | 2009/2010<br>ICROPROCE<br>ICROCONTF                                         | SSOR AND                                                                  | EXAMIN        |               |              | E : 3 BEE<br>CT CODE : BI | EE 3233      |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------|---------------|--------------|---------------------------|--------------|

|                    | 141                                                                                                                            |                                                                             |                                                                           | of PIC16      |               | ·<br>16C71   |                           |              |

|                    | OPTION Register of PIC16F84A / PIC16C71<br>R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 F                                                     |                                                                             |                                                                           |               |               |              |                           |              |

|                    | R/W-1<br>RBPU                                                                                                                  | R/W-1<br>INTEDG                                                             | R/W-1<br>T0CS                                                             | R/W-1<br>T0SE | R/W-1<br>PSA  | R/W-1<br>PS2 | PS1                       | R/W-1<br>PS0 |

|                    | bit 7                                                                                                                          | INTEDO                                                                      | 1000                                                                      | TOOL          |               | 1.02         |                           | bit 0        |

| bit 7              | 1 = PORT                                                                                                                       | RTB Pull-up<br>B pull-ups al<br>B pull-ups al                               | e disabled                                                                | y individual  | port latch va | alues        |                           |              |

| bit 6              | INTEDG: In<br>1 = Interru                                                                                                      | nterrupt Edg<br>pt on rising<br>pt on falling                               | e Select bit<br>edge of RB0                                               | )/INT pin     |               |              |                           |              |

| bit 5              | <b>TOCS</b> : TMR0 Clock Source Select bit<br>1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT) |                                                                             |                                                                           |               |               |              |                           |              |

| bit 4              | 1 = Incren                                                                                                                     | R0 Source E<br>nent on high-<br>nent on low-f                               | to-low trans                                                              | ition on RA   |               |              |                           |              |

| bit 3              | 1 = Presca                                                                                                                     | caler Assign<br>aler is assigr<br>aler is assigr                            | ned to the W                                                              |               | le            |              |                           |              |

| bit 2-0            |                                                                                                                                | Prescaler Ra<br>TMR0 Rate                                                   |                                                                           |               |               |              |                           |              |

|                    | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                           | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 |               |               |              |                           |              |

|                    |                                                                                                                                |                                                                             |                                                                           |               |               |              |                           |              |

#### **FINAL EXAMINATION** COURSE : 3 BEE SEMESTER/SESSION : I/2009/2010 : MICROPROCESSOR AND SUBJECT CODE : BEE 3233 SUBJECT MICROCONTROLLER **INTCON Register of PIC16F84A** R/W-0 R/W-x R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 INTF TOIE TOIF RBIF GIE EEIE INTE RBIE bit O bit 7 bit 7 GIE: Global Interrupt Enable bit 1 = Enables all unmasked interrupts o = Disables all interrupts EEIE: EE Write Complete Interrupt Enable bit bit 6 1 = Enables the EE Write Complete interrupts o = Disables the EE Write Complete interrupt TOIE: TMR0 Overflow Interrupt Enable bit bit 5 1 = Enables the TMR0 interrupt o = Disables the TMR0 interrupt INTE: RB0/INT External Interrupt Enable bit bit 4 1 = Enables the RB0/INT external interrupt o = Disables the RB0/INT external interrupt RBIE: RB Port Change Interrupt Enable bit bit 3 1 = Enables the RB port change interrupt o = Disables the RB port change interrupt bit 2 TOIF: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software) o = TMR0 register did not overflow INTF: RB0/INT External Interrupt Flag bit bit 1 1 = The RB0/INT external interrupt occurred (must be cleared in software) o = The RB0/INT external interrupt did not occur bit O **RBIF:** RB Port Change Interrupt Flag bit 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software) o = None of the RB7:RB4 pins have changed state

#### BEE 3233 **FINAL EXAMINATION** SEMESTER/SESSION : I/2009/2010 COURSE : 3 BEE SUBJECT : MICROPROCESSOR AND SUBJECT CODE : BEE 3233 MICROCONTROLLER Special Function Register (SFR) File Summary for PIC16C71 Value on all Value on: Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Address Name Bit 0 POR. other resets BOR (1) Bank 0 00h(3) INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000 01h TMRO Timer0 module's register XXXX XXXX uuuu uuuu 0000 0000 02h<sup>(3)</sup> PCL Program Counter's (PC) Least Significant Byte 0000 0000 IRP(5) RP1(5) 03h(3) STATUS PD z DC С 000q quuu RP0 то 0001 1xxx 04h(3) FSR Indirect data memory address pointer XXXX XXXX uuuu uuuu 05h PORTA PORTA Data Latch when written: PORTA pins when read ---x 0000 ---u 0000 06h PORTB PORTB Data Latch when written: PORTB pins when read XXXX XXXX uuuu uuuu 07h Unimplemented -GO/DONE 08h ADCONO ADCS1 ADCS0 (6) CHS1 CHSO ADIF ADON 00-0 0000 00-0 0000 09h<sup>(3)</sup> ADRES A/D Result Register XXXX XXXX uuuu uuuu ---0 0000 DAh(2.3) PCLATH Write Buffer for the upper 5 bits of the Program Counter --0 0000 TOIE 0Bh<sup>(3)</sup> INTCON GIE ADIE INTE RBIE TOIF INTE RBIF 0000 000x 0000 000u Bank 1 80h<sup>(3)</sup> INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000 OPTION RBPU INTEDG TOCS TOSE PS1 81h PSA PS2 PS0 1111 1111 1111 1111 82h<sup>(3)</sup> PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000 83h<sup>(3)</sup> STATUS IRP(5) RP1(5) RP0 то DQ z DC С 0001 1xxx 000q quuu 84h(3) FSR Indirect data memory address pointer XXXX XXXX uuuu uuuu 85h TRISA -PORTA Data Direction Register ---1 1111 ---1 1111 86h TRISB 1111 1111 1111 1111 PORTB Data Direction Control Register 87h<sup>(4)</sup> ---- --qq PCON ----POR BŌR ---- uu 88h ADCON1 PCFG1 PCFG0 ---- --00 ---- --00 89h<sup>(3)</sup> ADRES A/D Result Register XXXX XXXX uuuu uuuu 8Ah(2.3) PCLATH ---0 0000 Write Buffer for the upper 5 bits of the Program Counter ---0 0000 --x000 000x 8Bh<sup>(3)</sup> INTCON GIE ADIE TOIE INTE RBIE TOIF INTE RBIF 0000 000u x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Legend: Shaded locations are unimplemented, read as '0'. Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose 2: contents are transferred to the upper byte of the program counter. 3: These registers can be addressed from either bank. The PCON register is not physically implemented in the PIC16C71, read as '0'. 41 The IRP and RP1 bits are reserved on the PIC16C710/71/711, always maintain these bits clear. 5:

6: Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is unimplemented, read as '0'.

|                      | FINAL EXAMINAT                                                                                                                                                                                                                                                                                                                               | FION                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| EMESTI<br>UBJECT     | R/SESSION : I/2009/2010<br>: MICROPROCESSOR AND<br>MICROCONTROLLER                                                                                                                                                                                                                                                                           | COURSE : 3 BEE<br>SUBJECT CODE : BEE 3233                                                                                   |

|                      | STATUS Register of Pl                                                                                                                                                                                                                                                                                                                        | IC16C71                                                                                                                     |

| R/W-0<br>IRP<br>bit7 |                                                                                                                                                                                                                                                                                                                                              | M-x R/W-x<br>bit0 R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:               | <b>IRP:</b> Register Bank Select bit (used for indirect addressi<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                                                 |                                                                                                                             |

| bit 6-5:             | <b>RP1:RP0:</b> Register Bank Select bits (used for direct add<br>11 = Bank 3 (180h - 1FFh)<br>10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes                                                                                                                                     | dressing)                                                                                                                   |

| bit 4:               | <b>TO:</b> Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruct<br>0 = A WDT time-out occurred                                                                                                                                                                                                                          | ction                                                                                                                       |

| bit 3:               | <b>PD:</b> Power-down bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                                                                                    |                                                                                                                             |

| bit 2:               | <b>Z</b> : Zero bit<br>1 = The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not z                                                                                                                                                                                             |                                                                                                                             |

| bit 1:               | <b>DC:</b> Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF $1 = A$ carry-out from the 4th low order bit of the result of 0 = No carry-out from the 4th low order bit of the result                                                                                                                                                        |                                                                                                                             |

| bit O:               | <b>C</b> : Carry/borrow bit (ADDWE ADDLW, SUBLW, SUBWF instruct $1 = A$ carry-out from the most significant bit of the result $0 = No$ carry-out from the most significant bit of the result Note: For borrow the polarity is reversed. A subtraction the second operand. For rotate (RRF, RLF) instructions, to bit of the source register. | t occurred<br>ult occurred<br>is executed by adding the two's complement of                                                 |

|                      |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                             |

| TFR/SFSSI                                      | on : 1/2009                                            | 0/2010        | FINA.                                   | L EXAM        | INATION           | N                       | COURSE : 3 BEE                                                            |  |  |

|------------------------------------------------|--------------------------------------------------------|---------------|-----------------------------------------|---------------|-------------------|-------------------------|---------------------------------------------------------------------------|--|--|

| JBJECT : MICROPROCESSOR AND<br>MICROCONTROLLER |                                                        |               |                                         |               |                   | SUBJECT CODE : BEE 3233 |                                                                           |  |  |

|                                                |                                                        |               | INTCON                                  | Register      | of PIC16          | C71                     |                                                                           |  |  |

| R/W-0<br>GIE<br>bit7                           | R/W-0<br>ADIE                                          | R/W-0<br>T0IE | R/W-0                                   | R/W-0<br>RBIE | R/W-0<br>T0IF     | R/W-0                   |                                                                           |  |  |

| bit 7:                                         | <b>GIE:<sup>(1)</sup> GI</b><br>1 = Enabl<br>0 = Disab | es all un     | masked in                               |               |                   | v.<br>U                 | = Readable bit<br>/ = Writable bit<br>= Unimplemented bit.<br>read as '0' |  |  |

| bit 6:                                         | ADIE: A/D<br>1 = Enabl<br>0 = Disab                    | es A/D ir     | terrupt                                 | pt Enable I   | bit               | -                       | n = Value at POR reset                                                    |  |  |

| bit 5:                                         | 1 = Enabl                                              | es the TI     | low Interru<br>MR0 interr<br>MR0 interr | upt           | bit               |                         |                                                                           |  |  |

| bit 4:                                         | 1 = Enabl                                              | es the R      | ternal Inte<br>B0/INT ext<br>80/INT ex  | ernal inter   | rupt              |                         |                                                                           |  |  |

| bit 3:                                         | 1 = Enabl                                              | es the R      | ange Inter<br>B port cha<br>RB port cha | nge interri   | upt               |                         |                                                                           |  |  |

| bit 2:                                         | 1 = TMR0                                               | register      | low Interru<br>has overfl<br>did not ov | owed (mu      | t<br>st be cleare | ed in soft              | ware)                                                                     |  |  |

| bit 1:                                         | 1 = The F                                              | B0/INT (      |                                         | terrupt occ   |                   | t be clea               | ared in software)                                                         |  |  |

| bit 0:                                         | 1 = At lea                                             | st one of     |                                         | RB4 pins o    |                   | •                       | t be cleared in software)                                                 |  |  |

|                                                |                                                        |               |                                         |               |                   |                         |                                                                           |  |  |

|                                                |                                                        |               |                                         |               |                   |                         |                                                                           |  |  |

| EMESTER/SESSION : I/2009/2010COURSE : 3 BEEJBJECT : MICROPROCESSOR AND<br>MICROCONTROLLERSUBJECT CODE : BEE 3233 |                                                             |                                        |                            |               |                                     |               |                       |                                                                  |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------|----------------------------|---------------|-------------------------------------|---------------|-----------------------|------------------------------------------------------------------|

|                                                                                                                  |                                                             |                                        | AD                         | CON0 I        | Register of I                       | PIC16C7       | '1                    |                                                                  |

| R/W-0<br>ADCS1<br>bit7                                                                                           | R/W-0<br>ADCS0                                              | U-0<br>(1)                             | R/W-0<br>CHS1              | R/W-0<br>CHS0 | R/W-0<br>GO/DONE                    | R/W-0<br>ADIF | R/W-0<br>ADON<br>bit0 | R = Readable bit<br>W = Writable bit                             |

|                                                                                                                  | <b>ADCS1:A</b><br>00 = Fosc<br>01 = Fosc                    | /2                                     | ) Conversi                 | on Clock S    | Select bits                         |               |                       | U = Unimplemented<br>bit, read as '0'<br>- n =Value at POR reset |

| bit 5:                                                                                                           | 10 = Fosc<br>11 = FRC (<br>Unimplem                         | /32<br>clock deri                      |                            | n RC osci     | llation)                            |               |                       |                                                                  |

| bit 4-3:                                                                                                         | CHS1:CH<br>00 = chan<br>01 = chan<br>10 = chan<br>11 = chan | nel 0, (RA<br>nel 1, (RA<br>nel 2, (RA | 0/AN0)<br>1/AN1)<br>2/AN2) | Select bit    | 5                                   |               |                       |                                                                  |

| bit 2:                                                                                                           |                                                             | <u>1</u><br>nversion i<br>pnversion    | n progress                 | (setting t    | nis bit starts th<br>bit is automat |               |                       | vare when the A/D conver-                                        |

| bit 1:                                                                                                           | ADIF: A/D<br>1 = conver<br>0 = conver                       | sion is co                             | mplete (mu                 |               | ot Flag bit<br>Ired in softwar      | e)            |                       |                                                                  |

| bit 0:<br>Note 1:                                                                                                | Bit5 of AD                                                  | onverter m<br>onverter m<br>CON0 is    | odule is sh<br>a General   | utoff and     | consumes no<br>R/W bit for the      | •             |                       | For the PIC16C71, this bit                                       |

| Note 1:                                                                                                          | 0 = A/D cc                                                  | NVerter m                              | odule is sh<br>a General   | utoff and     |                                     | •             |                       | For the PIC16C71, this bit                                       |

| SUBJEC |                | /2009/2010<br>MICROPROCES<br>MICROCONTRO | SSOR AND       | XAMINA       |          |       | SE : 3 BEE<br>CT CODE : BEE 3233     |

|--------|----------------|------------------------------------------|----------------|--------------|----------|-------|--------------------------------------|

|        |                | A                                        | DCON1 R        | egister of l | PIC16C71 |       |                                      |

|        | ) U-0 L        | J-0 U-0                                  | U-0            | U-0          | R/W-0    | R/W-0 |                                      |

| L :47  |                |                                          | —              |              | PCFG1    | PCFG0 | R = Readable bit<br>W = Writable bit |

| bit7   |                |                                          |                |              |          | bit0  | U = Unimplemented                    |

|        |                |                                          |                |              |          |       | bit, read as '0'                     |

| hit 7  | 2. Unimplement | ad: Dood on 10                           | 1              |              |          |       | - n =Value at POR res                |

|        | 2: Unimplement |                                          |                | ontrol hito  |          |       |                                      |

| DIC 1- | 0: PCFG1:PCFG  | U: A/D Port Co                           | ninguration Co | DATION DITS  |          |       |                                      |

|        | PCFG1:PCFG0    | RA1 & RA0                                | RA2            | RA3          | VREF     |       |                                      |

|        | 00             | A                                        | A              | A            | VDD      |       |                                      |

|        | 01             | A                                        | A              | VREF         | RA3      |       |                                      |

|        | 10             | A                                        | D              | D            | VDD      |       |                                      |

|        | 11             | D                                        | D              | D            | VDD      |       |                                      |

|        |                |                                          |                |              |          |       |                                      |

## FINAL EXAMINATION

SEMESTER/SESSION : 1/2009/2010 SUBJECT : MICROPRO : MICROPROCESSOR AND

MICROCONTROLLER

COURSE : 3 BEE SUBJECT CODE : BEE 3233

# PIC16F84A Instruction Set Summary

| Mnem   |      | Description                  | Cycles    |       | 14-Bit ( | Opcode  | e    | Status   | Notes |

|--------|------|------------------------------|-----------|-------|----------|---------|------|----------|-------|

| Орега  | Inds | Description                  | Cycles    | MSb   |          |         | LSb  | Affected | notes |

|        |      | BYTE-ORIENTED FILE REG       | ISTER OPE | RATIC | NS       |         |      |          |       |

| ADDWF  | f, d | Add W and f                  | 1         | 00    | 0111     | dfff    | ffff | C,DC,Z   | 1.2   |

| ANDWF  | f, d | AND W with f                 | 1         | 00    | 0101     | dfff    | ffff | Z        | 1,2   |

| CLRF   | f    | Clear f                      | 1         | 00    | 0001     | lfff    | ffff | z        | 2     |

| CLRW   | -    | Clear W                      | 1         | 00    | 0001     | 0)2222  | xxxx | z        |       |

| COMF   | f, d | Complement f                 | 1         | 00    | 1001     | dfff    | ffff | z        | 1,2   |

| DECF   | f, d | Decrement f                  | 1         | 00    | 0011     | dfff    | ffff | z        | 1.2   |

| DECFSZ | f, d | Decrement f, Skip if 0       | 1 (2)     | 00    | 1011     | dfff    | ffff | -        | 1.2.3 |

| INCF   | f, d | Increment f                  |           | 00    | 1010     | dfff    | ffff | z        | 1.2   |

| INCFSZ | f, d | Increment f, Skip if 0       | 1 (2)     | 00    | 1111     | dfff    | ffff | _        | 1,2,3 |

| IORWF  | f, d | Inclusive OR W with f        |           | 00    | 0100     |         | ffff | z        | 1.2   |

| MOVE   | f, d | Move f                       | 1         | 00    | 1000     |         | ffff | z        | 1.2   |

| MOVWF  | f    | Move W to f                  | 1         | 00    | 0000     |         | ffff | -        | ···-  |

| NOP    | 1    | No Operation                 | 1         | 00    | 0000     | 0xx0    | 0000 |          |       |

| RLF    | f, d | Rotate Left f through Carry  | 1         | 00    | 1101     |         | ffff | c        | 1.2   |

| RRF    | f, d | Rotate Right f through Carry | 1         | 00    | 1100     |         | ffff | č        | 1,2   |

| SUBWF  | f, d | Subtract W from f            |           | 00    | 0010     |         | ffff | C.DC.Z   | 1.2   |

| SWAPF  | f, d | Swap nibbles in f            |           | 00    | 1110     |         | ffff | 0.00,2   | 1,2   |

| XORWF  | f, d | Exclusive OR W with f        | 1         | 00    | 0110     |         | ffff | z        | 1.2   |

|        |      | BIT-ORIENTED FILE REG        | STER OPE  | RATIO | NS       |         |      |          | ļ     |

| BCF    | f, b | Bit Clear f                  | 1         | 01    | 0.055    | bfff    | **** |          | 1.2   |

| BSF    | f, b | Bit Set f                    |           |       |          | bfff    |      |          | 1,2   |

| BTFSC  | f, b | Bit Test f, Skip if Clear    | 1 (2)     | 01    |          | bfff    |      |          | 3     |

| BTFSS  | f, b | Bit Test f, Skip if Set      | 1 (2)     |       |          | bfff    |      |          | 3     |

| 511.00 | 1, 0 | LITERAL AND CONTR            |           |       | 1100     | DIII    |      |          |       |

| ADDLW  | k    | Add literal and W            | 1         | 11    | 111×     | kkkk    | kkkk | C.DC.Z   |       |

| ANDLW  | k    | AND literal with W           |           | 11    | 1001     |         | kkkk | Z        |       |

| CALL   | k    | Call subroutine              |           | 10    | _        | kkkk    |      |          |       |

| CLRWDT | -    | Clear Watchdog Timer         | 1         | 00    | 0000     | 0110    | 0100 | TO.PD    |       |

| GOTO   | k    | Go to address                | 2         | 10    | 1kkk     |         |      |          |       |

| IORLW  | k    | Inclusive OR literal with W  | 1         | 11    | 1000     |         | kkkk | z        |       |

| MOVLW  | k    | Move literal to W            |           | 11    |          | kkkk    |      | - I      |       |

| RETFIE | -    | Return from interrupt        | 2         | 00    | 0000     | 0000    | 1001 |          |       |

| RETLW  | k    | Return with literal in W     | 2         |       |          | kkkk    |      |          |       |

| RETURN | -    | Return from Subroutine       | 2         |       | 0000     | 0000    | 1000 |          |       |

| SLEEP  | _    | Go into standby mode         | 1         |       | 0000     | 0110    | 0011 | TO,PD    |       |

| SUBLW  | k    | Subtract W from literal      |           | 11    |          | kkkk    | kkkk | C.DC.Z   |       |

| XORLW  | k    | Exclusive OR literal with W  |           |       | 1010     | kkkk    |      | Z        |       |

|        |      |                              | <u> </u>  | 1 11  | 1010     | K K K K | KKKK | <u> </u> |       |

## FINAL EXAMINATION

SEMESTER/SESSION : I/2009/2010 SUBJECT : MICROPROCESSOR AND MICROCONTROLLER COURSE : 3 BEE SUBJECT CODE : BEE 3233

# **Bcc (Branch Conditionally) Instruction**

| Instruction | Meaning                    | Arithmetic | If the test is true |

|-------------|----------------------------|------------|---------------------|

| BEQ         | EQual to zero              | U          | Z=1                 |

| BNE         | Not Equal to zero          | U          | Z=0                 |

| BMI         | Minus                      | U          | N=1                 |

| BPL         | Plus                       | U          | N=0                 |

| BCS LO      | Carry Set/LOwer            | U          | C=1                 |

| BCC/HS      | Carry Clear/Higher or Same | U          | C=0                 |

| BVS         | oVerflow Set               | S          | V=1                 |

| BVC         | oVerflow Clear             | S          | V=0                 |

| BGT         | GreaTer than               | S          | Z+(N⊕V)=0           |

| BLT         | Less Than                  | S          | N⊕V=1               |

| BGE         | Greater than or Equal      | S          | N⊕V=0               |

| BLE         | Less than or Equal         | S          | Z+(N⊕V)=0           |

| BHI         | Higher                     | U          | C+Z=0               |

| BLS         | Lower than or Same         | U          | C+Z=1               |

| LIEV    |              | ASCII Conversion Table |          |               |     |     |     |     |     |  |  |

|---------|--------------|------------------------|----------|---------------|-----|-----|-----|-----|-----|--|--|

| HEX     | MSD          | 0                      | 1        | 2             | 3   | 4   | 5   | 6   | 7   |  |  |

| LSD     | BITS         | 000                    | 001      | 010           | 011 | 100 | 101 | 110 | 111 |  |  |

| 0       | 0000         | NUL                    | DLE      | SPAC<br>E     | 0   | @   | Р   | -   | Р   |  |  |

| 1       | 0001         | SOH                    | DC1      | <u>E</u><br>! | 1   | Α   | Q   | a   | Q   |  |  |

| 2       | 0010         | STX                    | DC2      | 66            | 2   | B   | R   | b   | R   |  |  |

| 3       | 0011         | ETX                    | DC3      | #             | 3   | С   | S   | С   | S   |  |  |

| 4       | 0100         | EOT                    | DC4      | \$            | 4   | D   | Т   | d   | Т   |  |  |

| 5       | 0101         | ENQ                    | NAK      | %             | 5   | Е   | U   | е   | U   |  |  |

| 6       | 0110         | ACK                    | SYN      | &             | 6   | F   | V   | f   | V   |  |  |

| 7       | 0111         | BEL                    | ETB      |               | 7   | G   | W   | g   | W   |  |  |

| 8       | 1000         | BS                     | CAN      | (             | 8   | Н   | х   | h   | X   |  |  |

| 9       | 1001         | HT                     | EM       | )             | 9   | I   | Y   | i   | Y   |  |  |

| A       | 1010         | LF                     | SUB      | *             | :   | J   | Z   | j   | Z   |  |  |

| B       | 1011         | VT                     | ESC      | +             | ;   | К   | [   | k   | {   |  |  |

| C       | 1100         | FF                     | FS       |               | <   | L   | \   | 1   |     |  |  |

| D<br>E  | 1101<br>1110 | CR                     | GS       | -             | =   | M   | ]   | m   | }   |  |  |

| F       | 1110         | SO<br>SI               | RS<br>US | •             | > ? | N   |     | n   | ~   |  |  |

| <b></b> |              | 51                     | 05       | /             | ?   | 0   | -   | 0   | DEL |  |  |

|         |              |                        |          | <u> </u>      |     | 0   |     | 0   | DEL |  |  |