## **CONFIDENTIAL**

## **UNIVERSITI TUN HUSSEIN ONN MALAYSIA**

# FINAL EXAMINATION SEMESTER I SESSION 2012/2013

| COURSE NAME : CII | RCUIT THEORY |

|-------------------|--------------|

|-------------------|--------------|

- COURSE CODE : DEE 1223 / DAE 11103

- PROGRAMME : 1 DEE

EXAMINATION DATE : OCTOBER 2012

- DURATION : 3 HOURS

- INSTRUCTION : ANSWER FIVE (5) QUESTIONS ONLY.

THIS QUESTION PAPER CONSISTS OF TEN (10) PAGES

CONFIDENTIAL

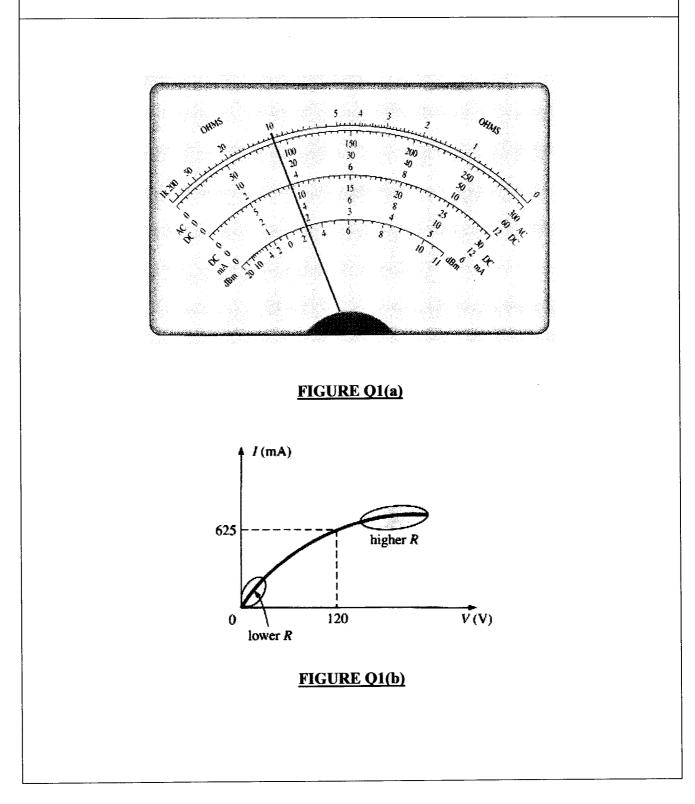

- Q1 (a) In Figure Q1(a), determine the quantity (voltage, current, or resistance) that is being measured and its value for each of the following specified switch settings on a typical analog multimeter.

- (i) DC volts: 60

- (ii) DC mA: 12

- (iii) OHMS: x1K

(6 marks)

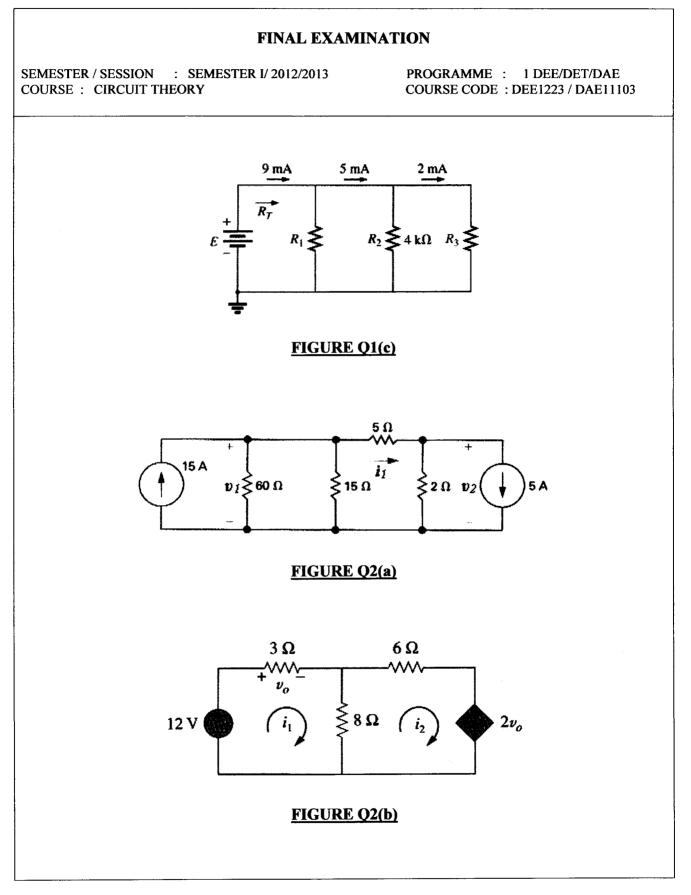

(b) The I-V characteristics of a light bulb are provided in Figure Q1(b). Note the nonlinearity of the curve, indicating a wide range in resistance of the bulb with applied voltage. If the rated DC voltage is 120 V, find the wattage rating of the bulb. Also calculate the resistance of the bulb under rated conditions.

(6 marks)

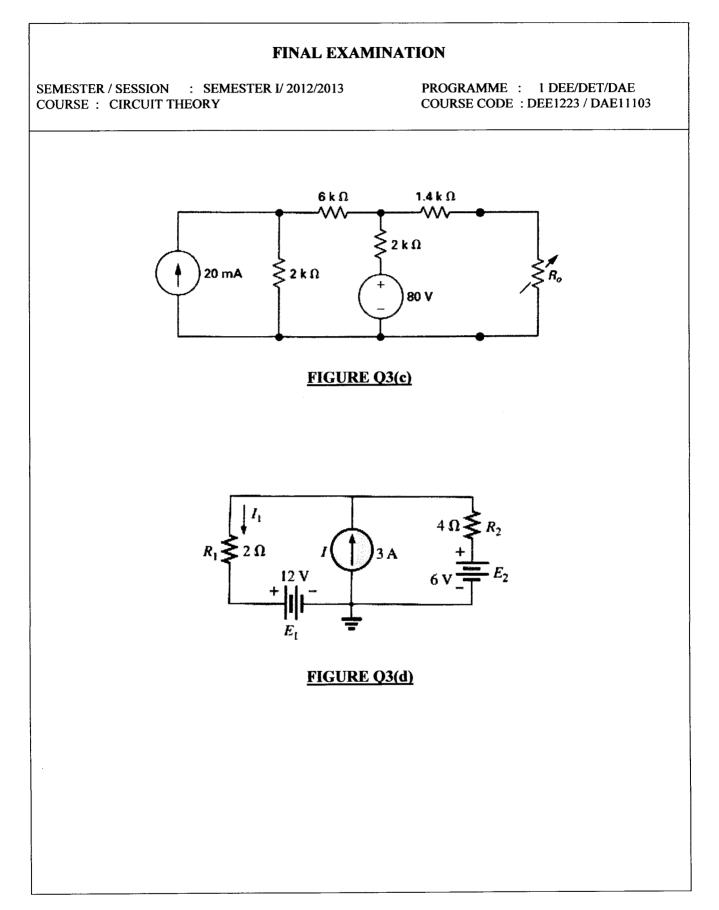

(c) Using the information provided in Figure Q1(c), find the branch resistors  $R_1$  and  $R_3$ , the total resistance  $R_T$ , and the voltage source E.

(8 marks)

Q2 (a) Use nodal analysis to find  $v_1$ ,  $v_2$ , and  $i_1$  for the circuit shown in Figure Q2(a).

(10 marks)

(b) Calculate the mesh currents  $i_1$  and  $i_2$  in Figure Q2(b) and determine the power dissipated in the 8  $\Omega$  resistor.

(10 marks)

Q3 (a) State the maximum power transfer theorem.

(2 marks)

(b) When is maximum power delivered from a source to a load?

(2 marks)

- (c) The variable resistor in the circuit in Figure Q3(c) is adjusted for maximum power transfer to  $R_o$ .

- (i) Find the value of  $R_o$ .

#### DEE 1223 /DAE 11103

(ii) Find the maximum power that can be delivered to  $R_o$ .

(8 marks)

(d) In superposition theorem, the presence of three sources results in three different networks to be analysed. Find the current  $I_1$  of the network in Figure Q3(d).

(8 marks)

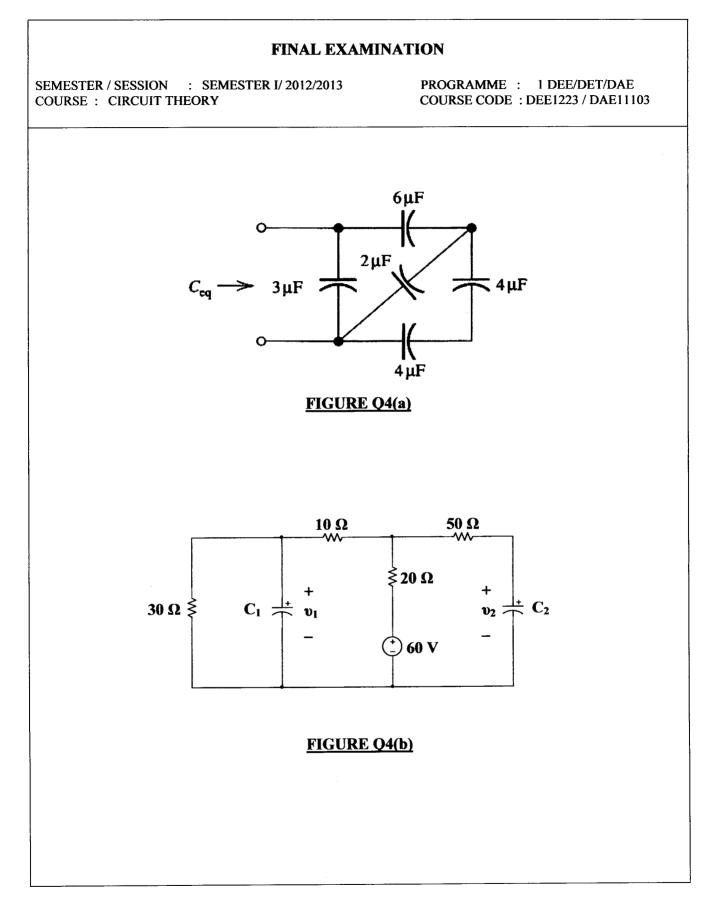

Q4 (a) Find the equivalent capacitance for the circuit shown in Figure Q4(a).

(4 marks)

(b) Determine the voltage across the capacitors in the circuit of Figure Q4(b) under DC conditions.

(8 marks)

(c) The current through a 12 mH inductor is known to be

$i_{\rm L} = 4 \sin 100t \, {\rm A} \qquad t > 0$

(i) Find the voltage across the inductor for t > 0

(ii) Find the energy stored in the inductor at  $t = \frac{\pi}{200} s$

(8 marks)

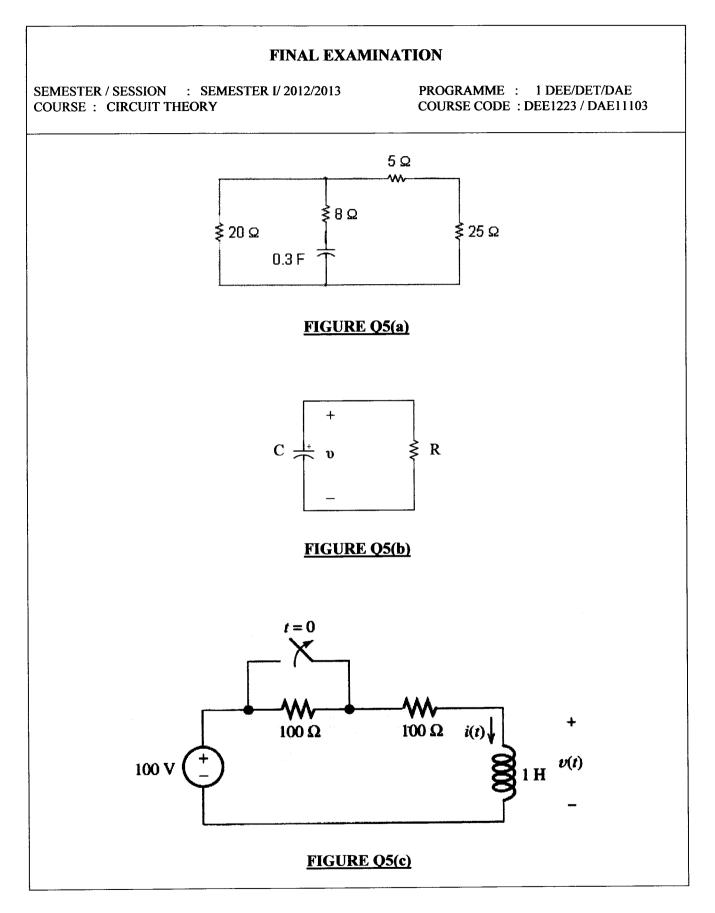

Q5 (a) Find the time constant of the circuit shown in Figure Q5(a).

(4 marks)

(b) In the circuit in Figure Q5(b), the voltage and current expressions are

$$v = 100e^{-1000t}$$

V,  $t \ge 0$

$i = 5e^{-1000t}$  mA,  $t \ge 0^+$

Find :

(ii) C

(iii)  $\tau$  (in milliseconds)

(iv) the initial energy stored in the capacitor

(8 marks)

(c) Consider the circuit shown in Figure Q5(c). Assume that the switch has been closed for a very long time prior to t = 0. Find expressions for i(t) and v(t).

(8 marks)

### Q6

(a)

- In a linear circuit, the voltage source is  $v_s = 12 \sin (10^3 t + 24^\circ) V$ .

- (i) What is the angular frequency of the voltage?

- (ii) What is the frequency of the source?

- (iii) Find the period of the voltage.

- (iv) Express  $v_s$  in cosine form.

- (v) Determine  $v_s$  at t = 2.5 ms.

(10 marks)

- (b) For the circuit shown in Figure Q6(b):

- (i) Find the total impedance  $Z_T$ .

- (ii) Determine the current  $I_S$ .

- (iii) Calculate  $V_R$  and  $V_C$ .

- (iv) Find  $I_C$

(10 marks)

- Q7 (a) The voltage across a load is  $v(t) = 160 \cos 377t$  V and the current through the element in the direction of the voltage drop is  $i(t) = 4 \cos (377t + 45^\circ)$  A. Find :

- (i) complex power

- (ii) apparent power

- (iii) real / average power

- (iv) reactive power

- (v) power factor and specify whether it is leading or lagging

(10 marks)

(b) A 50 kW load operates from a 60 Hz, 10 kV<sub>rms</sub> line with a power factor of 60% lagging. Compute the capacitance that must be placed in parallel with the load to achieve a 90% lagging power factor.

(10 marks)

SEMESTER / SESSION : SEMESTER I/ 2012/2013 COURSE : CIRCUIT THEORY PROGRAMME : 1 DEE/DET/DAE COURSE CODE : DEE1223 / DAE11103

6

### FINAL EXAMINATION

SEMESTER / SESSION : SEMESTER I/ 2012/2013 COURSE : CIRCUIT THEORY PROGRAMME : 1 DEE/DET/DAE COURSE CODE : DEE1223 / DAE11103